智能卡抗DPA攻擊的設計與實現

文章出處:http://www.nyfzw.net 作者:張劍峰 錢晶晶 談慧宇 高進濤 人氣: 發表時間:2011年09月29日

0 引 言

隨著個人計算機的蓬勃發展、因特網的演進與電子商務的沖擊,市場對安全與個人隱私保護有了強烈的需求。智能卡擁有輕便與安全的特性,在網絡上的安全付款、網絡連接的安全控管與電子簽章等應用領域扮演重要角色。我國已有不少信息安全應用系統借助智能卡來記憶系統運作所需的秘密信息,并利用智能卡具有的計算能力提升系統安全,智能卡正逐步取代磁卡而廣泛應用于金融及其他相關產業。

隨著對智能卡的攻擊方法的不斷發展,特別是隨著近年來許多新型的攻擊智能卡技術被公開發表,智能卡的安全面臨巨大挑戰。這些攻擊技術能容易地以低價設備取得的信息,如電力消耗、執行時間、故障時的輸出與輸入行為、輻射、電力尖峰情形等信息攻擊智能卡。其中,差分功耗分析(Differential Power Analysis,DPA)就是一種很有效的能量攻擊方法,其主要是借助統計方法來提取與密鑰有關的信息,實現過程比較復雜,但對攻擊者的智能卡專業技術水平的要求并不是很高,DPA對智能卡中相關的內嵌加密算法的成功攻擊已經被廣泛報道。

智能卡是一種在發卡后可下載應用程序的公開平臺架構,所以為了防止偽卡與保護持卡人,智能卡必須具有高安全性和高可靠性。VISA國際組織規定智能卡必須符合最高的安全技術層次要求,不但其內嵌儲存體和總線上傳遞的數據都要求加密,而且智能卡至少要提供一個以上的對策防止簡單功耗分析(Simple Power Analysis,SPA)與DPA攻擊。

1 智能卡芯片架構

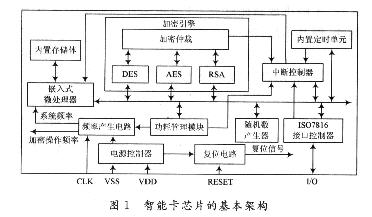

智能卡芯片架構如圖1所示,主要由如下模塊構成:

(1)嵌入式微處理器:可控制硬件執行相關的指令完成加解密操作。其一般內置有存儲器加解密單元,可通過其存取存儲體數據;并通過硬件防火墻管制應用程序存儲體。

(2)內置存儲體:智能卡的存儲體分為SRAM,E2PROM與ROM三塊區域,其中ROM存放智能卡操作系統、執行環境等程序及數據;E2PROM存放用戶定制代碼,給不同的用戶、不同的應用提供靈活的選擇;SRAM為執行系統操作提供臨時空間。

(3)復位電路:用于產生系統復位信號,其輸入來自RESET引腳輸入的外部復位信號。

(4)隨機數產生器:隨機數在智能卡的安全性上扮演著重要角色,密鑰生成、數字簽名、認證和鑒別及各種安全通信協議都離不開高質量的隨機數。該模塊主要產生無法預測的高質量加密用數據。

(5)ISO7816接口控制器:為智能卡與讀卡器數據交換的重要接口,主要是硬件支持由ISO7816制定的T=0及T=1兩種協議,T=0負責傳送字符(Charac-ter);T=1則負責傳送區塊(Block)。

(6)中斷控制器:用來接收定時單元、加密引擎、接口控制器的中斷要求,并傳送“中斷”信號給微處理器,通知微處理器外圍模塊已完成指定工作或有事情發生。

(7)內置定時單元:主要當作看門狗定時器用,用以監督系統的運作,監控內部應用程序是否正確執行。若發現程序運行錯誤,就會給中斷控制器一個中斷信號,使智能卡進入暫停狀態,一直要等到重置信號出現才恢復正常運行。

(8)電源控制器:內置的電壓傳感器和控制電路為其他模塊提供穩定、安全的電源供應。

(9)功耗管理模塊:智能卡對功耗的要求很高,該模塊是為達到節省電源的目的設計的省電裝置,其帶有停止和省電兩種工作模式。其中,停電模式支持ISO7816-3的頻率停止模式,以降低整個系統的電源消耗;省電模式則根據系統不同模塊工作特點規劃了各模塊的工作順序及狀態,使工作時間互斥的模塊中的一部分工作時,另一部分工作在睡眠狀態,從而達到降低系統整體功耗的目的。

(10)頻率產生電路:智能卡作為一個復雜的SoC芯片,其系統工作頻率和加密操作頻率是不同的,為此一般的智能卡內部都有PLL頻率產生電路。其頻率來自CLK腳輸入的外部頻率,產生供微處理器與加密引擎中各種加密協處理器使用要求的頻率。

(11)加密引擎:智能卡的加密引擎中嵌入了能實現多種加密算法的協處理器核,使其可以支持一般的加密算法包括:RSA,DES,AES。該模塊主要包括:

加密仲裁 根據系統不同用途下的不同加密操作要求,通過相關的控制指令管理不同的協處理器工作。DES協處理器 支持數據加密標準(Data E-ncryption Standard,DES)。以56 b密鑰為基礎的密碼塊加密技術,DES使用56 b密鑰對64 b的數據塊進行加密,并對64 b的數據塊進行16輪編碼,結果為64 b的密文。

AES協處理器 支持高級數據加密標準(Ad-Vanced Encryption Standard,AES)。使用的是一個迭代型分組密碼,對加密來說,輸入是一個明文分組和一個密鑰,輸出是一個密文分組;分組長度和密碼長度都可變,可以獨立指定為128 b,192 b或256 b。

RSA協處理器 支持公開金鑰加解密系統。RSA主要是指數的運算,是基于大質數的因數分解的公匙體系,簡單來講就是兩個很大的質數,一個作為公鑰,另一個作為私鑰,如用其中一個加密,則用另一個解密。密鑰長度從40~2048 b可變,密鑰越長,加密效果越好,但加密、解密的開銷也就越大。

智能卡的ASIC設計,主要模塊如加密引擎中所涉及的加解密協處理器、嵌入式微處理器等在市場上都由相關的IP核提供,這些IP的設計都采用了相關算法實現了抗DPA攻擊,具有很好的安全性。但是將上述IP整合及其他模塊的設計上必須注意采取抗DPA攻擊措施,才能保證智能卡的高安全性。

2 DPA攻擊原理

在一個沒有任何抗DPA攻擊的加密芯片上指令的執行順序和相關數據處理操作會影響功率消耗,盡管這種影響會被噪聲消耗,但是靠統計的方式還是可以看出端倪。DPA攻擊技術以功率消耗圖為基礎,再以統計方式推演主密鑰的攻擊技術,其原理是智能卡在執行加密過程中會消耗能量,產生電磁輻射,通過使用特殊的電子測量儀和數學統計技術,就可以檢測和分析這些變化,從而得到芯片中的特定關鍵信息。智能卡執行一條指令消耗的能量與指令的操作數相關,某一指令I的執行所消耗的平均功耗P如下式所示:

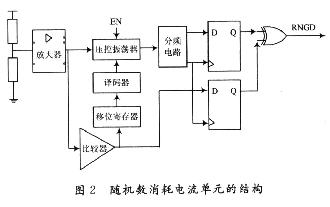

式中:PI表示指令I執行過程中平均消耗的能量;op1,op2,…,opn表示I的操作數;PI(0)和PI(1)分別表示op1取0和1時執行指令I消耗的平均功耗。可見,PI與op1相關(△PI≠0)。

另外,考慮到智能卡采用的是CMOS工藝,其功耗主要是動態功耗Pd,而Pd大小如下面公式所示:

![]()

式中:f是工作頻率;CL是輸出節點的集總負載電容;VDD是電源電壓;α是電路開關活動因子(電路翻轉率)。可見CMOS邏輯門功耗大小與α密切相關,所以,電路中的數據的0與1狀態與電路的功率信號必然具有一定的相關性。

綜上所述,加密用密鑰與電路功耗存在相關性,DPA攻擊就是從這種相關性人手,最終實現對密鑰的破解。下面以AES算法為例,介紹DPA攻擊的過程:

(1)隨機生成大量明文;

(2)加密這些明文,并記錄下加密操作時的能耗曲線,求得這些曲線的平均;

(3)關注第一輪S2盒的輸出,設輸出的第一比特為b,對第一輪子密鑰的第一個字節進行猜測,并用其與相應的明文計算出S2盒的輸出;

(4)根據b的值,將能耗曲線按照b=0和b=1分為兩類;

(5)計算出這兩類的平均能耗曲線,并將二者相減,求得差分能耗曲線;

(6)觀察步驟(2)和(5)生成的能量曲線。若密鑰猜測正確,那么步驟(4)的分組就是正確的,步驟(5)生成的差分能耗曲線將和步驟(2)生成的平均能耗曲線呈現較大的差別,差分能耗曲線中將出現峰值。因此,攻擊者通過觀察峰值來判斷密鑰的猜測是否正確;

(7)重復步驟(3)~(6),得到其他輪的子密鑰。DPA攻擊易于實現,一個完全不懂得智能卡技術的編程人員完全可以利用專用程序對沒有DPA防范的智能卡實現攻擊。高安全性的智能卡必須采取相應的防范措施以實現抗DPA攻擊。

3 抗DPA攻擊的設計

目前各種密碼系統的算術邏輯運算單元的VLSI設計已得到較為廣泛的研究,如何在其他方面實現抗DPA攻擊是值得進一步深入研究的問題。下面從隨機數產生器、組合和時序邏輯防DPA設計介紹智能卡抗DPA攻擊的電路實現。

3.1 隨機數產生器設計

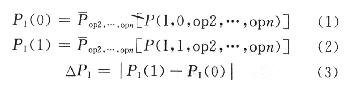

對于智能卡的DPA攻擊,主要是利用在卡上嵌入式微處理器運作時,某個特定指令的執行或數據存取所消耗功率,在供應電壓源上所表現特定的電流頻譜提供的有用信息。故可以通過外加額外的電路造成額外的電流消耗,從而改變電流頻譜以達到抗DPA攻擊。同時額外的電流消耗電路必須通過采用隨機數隨機的方式,產生隨機數消耗電流,以達到芯片消耗電力無法預測性,使其不能被分析與統計。

為此,可以在隨機數產生電路中設計如圖2所示的隨機數消耗電路,電路由比較器、移位寄存器、譯碼器組成;當電阻噪聲產生的噪聲電壓經過放大器、比較器后,產生“1”或“0”數字信號,存入移位寄存器,這樣寄存器內的值已經類似混沌式RNG所產生的隨機數,此隨機數經譯碼器編碼后,控制三態充放電緩沖器的充放電個數,最終達到以隨機數控制電流消耗的目的。

3.2 組合邏輯防DPA攻擊設計

防DPA攻擊的主要目的是使電路特性在運算時保持相同,而保持電特性相同很重要的一點是使翻轉的晶體管數量在任何運算步驟中都是一個常數。為實現這個目的可在電路運算步驟之間增加一個中間步驟,這樣能防止有用信息從功耗分析中泄漏出去。最簡單的中間步驟設置是在輸入參數和電路運算完成之后設置系統中間值。

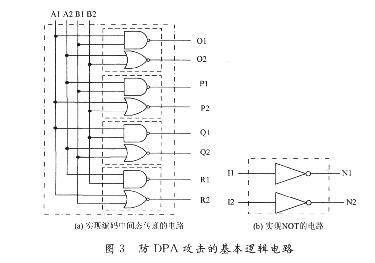

為此,參考異步邏輯電路的雙軌編碼方式中對信息的每一位用兩根信號線進行編碼的方式。采用兩位信號線的組合值“01”和“10”來表示數字邏輯的“真”和“假”,而組合值“00”和“01”則為中間值。這樣的編碼方式下,設計的基本邏輯單元電路如圖3所示。

如圖3(a)電路對于輸入A(A1A2)和B(B1B2),輸出只有O1O2和R1R2有效,當輸入A1A2B1B2為0000或1111時,輸出O1O2和R1R2的值是11或00,這樣實現了編碼中間態的傳遞。而當輸入A1A2B1B2為有效數據0101,0110,1001和1010時,輸出O1O2和R1的值就得到相關的NAND,AND,NOR和OR四個邏輯功能;其中,輸出O1O2→NAND,O2O1→AND,R1R2→NoR,R2R1→OR。至于NOT的實現如圖3(b)的電路所示。所以,上述基本的邏輯電路足以實現復雜的數字組合邏輯運算功能。

3.3 時序邏輯防DPA攻擊設計

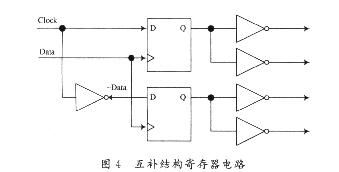

針對差分功耗分析,除了利用增加電路噪聲以降低差分功耗分析的信噪比的防御方案外。通過減小差分功率信號的值,同樣可以降低差分功耗分析的信噪比;若電路不同狀態下的功率差異趨于零,則差分功耗分析將失效。于是基于上述思路,在時序邏輯電路設計上可采用如圖4所示的互補結構寄存器電路。

設寄存器初始狀態相同,輸出負載相同,時鐘沿賦值,如圖4不論輸入為O或1,兩個互補寄存器必是一個翻轉,另一個不翻轉,因此總的功耗在兩種情況下沒有差別。

另外,對于采用前面所述的雙線信號編碼方式,在時序邏輯電路的設計上,可采用在輸入任何有效的數據01和10之前,都先把寄存器設置為00或11中間態的協議。這樣,無論進行何種操作,則時序邏輯中相關的寄存器都只有一個寄存器翻轉,有效地防止了寄存器在數據傳輸過程中的信息泄漏。

4 結 語

智能卡是一種高安全性、高可靠性和復雜的片上系統,具有抗功率分析攻擊、時間分析攻擊和故障分析攻擊的能力,但在一些新型的智能卡攻擊技術下其安全受到巨大的挑戰,例如DPA攻擊。本文針對DPA攻擊智能卡的特點,在智能卡的硬件電路上進行了抗DPA攻擊的設計,采用此設計,再結合一些軟件上的抗DPA攻擊措施,就能構成一個完善的智能卡安全體系結構,能十分有效地保證智能卡免受DPA攻擊。