智能卡芯片的發展及其所形成的設計方法

文章出處:http://www.nyfzw.net 作者:許珊琳 人氣: 發表時間:2011年09月18日

一、 智能卡的組成及發展

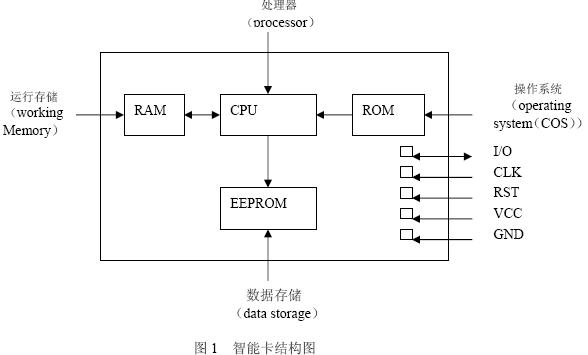

1.1 智能卡的基本組成

“中央處理單元(CPU)(或早期的中央控制邏輯)+ 各種存儲器(ROM/RAM/EEPROM) + 通訊接口”就形成了智能卡的基本功能。

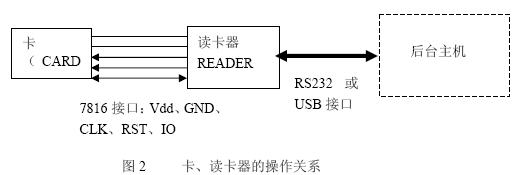

1.2 智能卡與讀卡器的操作

以接觸卡為例,讀卡器給卡供電源、時鐘信號、復位信號,IO 是雙向數據信號線,讀卡器和卡都通過IO 進行數據交換。在智能卡與讀卡器的相互操作過程中,讀卡器總是作為主動一方,卡作為被動的一方,所有的交易都是以讀卡器發命令開始,卡完成有關操作,并應答作為結束。

1.3 智能卡的發展

智能卡的結構框圖。

可以從結構、加密、通訊接口、CPU 體系結構、安全性設計、功耗降低以及供電電壓等,了解智能卡的發展。

1.3.1 結構

卡的發展經歷了從邏輯加密卡(memory 卡)->智能卡(CPU 卡)的發展。

早期的卡一般是所謂的邏輯加密卡,即卡內沒有CPU,只有一些安全邏輯、EEPROM 數據存儲器、通訊接口等單元,其優點是針對特定的安全算法、應用,可以做比較細致的設計優化;其缺點是不靈活,邏輯都是固定的,所有的功能都由硬件實現。

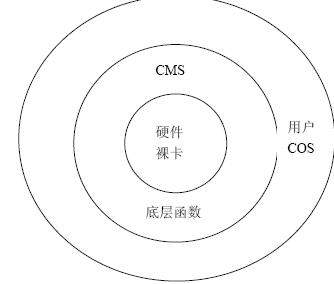

隨著集成電路設計的發展,允許在一個較小的面積內集成更多的電路,真正的智能卡——卡內嵌入了CPU,并引入COS——才形成,嚴格意義上的智能卡是內嵌CPU 的卡。由于在智能卡中,卡芯片本身只是一個硬件平臺,應用開發工程師開發針對不同應用的COS 也就形成了不同的卡,實現了硬件與軟件的分離,給應用實現帶來了極大的靈活性,形成了不同的邏輯抽象層次,芯片設計工程師可以在已定義的接口范圍內優化芯片設計,COS 開發工程師著重考慮應用實現。

1.3.2 加密算法

簡單的硬件加密邏輯—>對稱加密算法(DES、AES 等)—>PKI 算法(RSA、ECC 等)

安全加密算法是智能卡的必要組成部分,是實現智能卡認證和加密功能的基礎。

在邏輯加密卡階段,一般都是采用一些私有的加密算法,即算法不公開。對應的讀卡器也采用相應的算法,形成一套封閉系統。這種系統的安全性更多是依賴于對私有加密算法的保密來保證。

智能卡加密算法的發展引入了對稱加密算法,典型的有國際通用的DES,以及其升級版AES。對稱加密算法的算法本身是公開的,安全性依賴于密鑰的保密來保證。由于算法是公開的,卡、讀卡器的實現可以獨立進行,從這個意義上來說,系統是開放的。

對稱算法具有密鑰管理相對困難、不具有不可抵賴性等特點。在電子商務、電子政務等應用中不能滿足應用需求。在這種情況下,智能卡內嵌入了PKI 算法,形成了PKI 智能卡。比較通用的PKI 算法有RSA、ECC 等。公鑰算法的算法也是公開的,公鑰也公開,只要求保證私鑰的保密。

智能卡內嵌入了PKI 算法,并不表明智能卡就不需要對稱算法了。由于PKI 算法的計算量相對還是很大,運算速度相對對稱算法也比較慢,所以PKI 加密系統更多應用在數字簽名、對稱算法密鑰的傳輸加密等方面;而對稱算法加密系統更多應用在認證、大量數據的加密傳輸等方面。在目前階段,對稱加密系統、PKI 系統各有千秋,缺一不可。

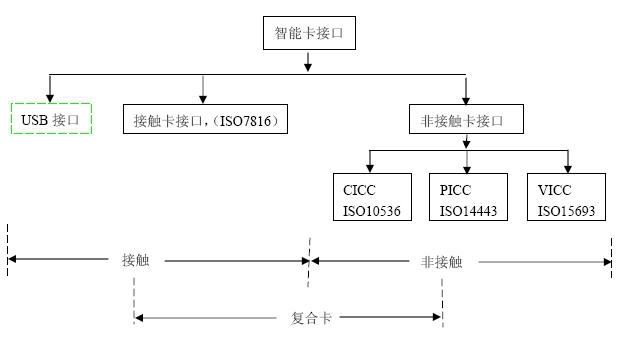

1.3.3 通訊接口

接觸卡接口(ISO7816)、非接觸卡接口(ISO14443,包括TYPE_A和TYPE_B;甚至一些RFID 等)、USB 接口(reader_less),現階段已經發展到一個芯片中集成了多種通訊接口,形成所謂的雙界面卡(接觸/非接觸、7816 接口/USB 接口等組合)。

從最開始的接觸卡接口,隨著應用的推廣及集成電路設計水平的提高,智能卡所能完成的功能越來越復雜,速度越來越快。ISO7816 的通訊速度就成為了智能卡交易的瓶頸,雖然可以采用高波特率的通訊模式,并且提高讀卡器供給智能卡的時鐘頻率等多種方法以提高智能卡的通訊效率。但是還是遠遠沒有能滿足實際應用的要求,尤其是在PKI 應用環境,隨著智能卡所處理的數據量的增大,通訊時間已經增加到約占智能卡處理時間的1/3 的程度,矛盾越來越突出。在這種情

況下,就產生了所謂的USB KEY 這樣一種特殊的智能卡形式,也就是在智能卡內直接嵌入了一個符合USB 規范的通訊接口。這樣卡就可以直接與計算機相連接,并進行交易,大大地提高了智能卡的處理效率。由于這種形式的USB KEY 直接與主機通訊,不需要讀卡器,通常也稱為“reader_less”卡。在目前階段,USB KEY 還沒有成為一個國際標準,但是據分析,USB 接口很可能會成為ISO7816 規范的一個可選接口,從而納入ISO7816 規范。

接觸卡接口由于有觸點的物理接口,屬于機械接觸。在實際應用中,存在一個機械壽命的問題。另外,在公共交通應用中,接觸卡接口還具有其固有的一系列技術限制。而非接觸卡則具有潛在的優勢,能解決接觸卡接口所固有的限制問題。非接觸卡不需要把卡插入到讀卡器的卡槽內,而且卡操作時對卡的方向性沒有要求,易于操作。隨著一些關鍵設計技術的成熟,非接觸卡的使用范圍正在迅速擴大,并且必將越來越大,尤其是在公共交通、物流管理等方面。

智能卡接口發展的一個有趣的形式是雙界面卡(也叫復合卡),在一個卡內集成了兩個不同的通訊接口,既可以是“ISO7816+USB”方式,也可以是“ISO7816+非接觸接口”形式。

但是智能卡接口的多樣性,并沒有從本質上改變智能卡的功能及特性,智能卡的核心功能沒有改變。

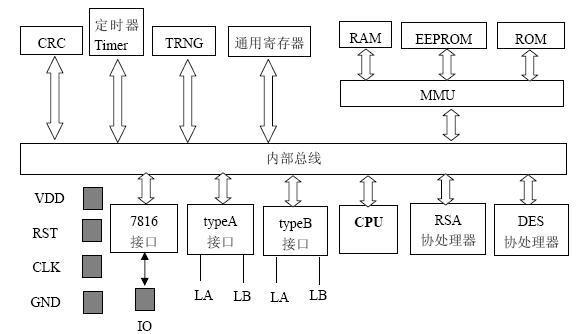

1.3.4 智能卡CPU 體系結構的發展

作為智能卡引擎的CPU 也在不斷的發展。早期智能卡內的CPU 與普通的嵌入式微控制器沒有太多的區別,僅僅是一個CPU 核而已。但是隨著智能卡安全性、多用途等需求的不斷提高,智能卡內CPU 的體系結構也相應地發生了很大的變化。除了必須具有通用嵌入式微控制器的各種特性外,更多的是表現在安全性能方面逐步形成為一個特定的、安全的智能卡CPU 核。

智能卡特定的、安全的 CPU 核可以從以下幾方面得到體現。

1、 CPU 支持多個狀態,比如系統態或內核態、用戶態。不同狀態的權限定義不同,處在系統態的程序可以操作(讀/寫)所有的硬件資源;處在用戶態的程序只能操作(讀或寫或讀/寫)有限的硬件資源(根據權限的定義)。

2、 CPU 指令執行時間(指令周期)的隨機化。

3、 中斷系統支持CPU 狀態的轉換,從而實現不同層次的安全級別控制,支持多應用的實現。

4、 MMU 系統;邏輯地址、物理地址的隔離;及地址映射,從體系結構上支持應用(多應用)、安全性的設計實現,與CPU 不同狀態一起有機的組成一個硬件防火墻。

5、 中斷系統、定時器(timer)可以認為是智能卡特定的CPU 的基本組成部分。隨著智能卡的發展,許多功能的實現(尤其是PKI算法的實現)都是軟、硬件共同組成的,也就是說一些本來屬于芯片功能的設計可能會采用軟件(一般稱為系統函數庫)來實現。系統函數庫是芯片的一部分,是芯片廠商的知識產權,必須進行保護;同時也必須允許用戶(COS)使用。中斷系統能很好地支持系統函數庫與用戶程序COS 的接口及權限傳遞和切換。

6、 擴展的存儲器地址空間。智能卡發展到今天,64KB 的程序空間已經不能滿足應用需求。程序存儲器空間一般都支持20 以上的地址位寬。數據存儲器空間也支持64KB 范圍。SFR 地址范圍也達到128KB 或256KB。總體上,具有很好的擴展性。

7、 不揮發存儲器(EEPROM/EFLASH)從邏輯上被劃分為程序存儲器,以支持程序下載。

1.3.5 安全性設計

智能卡的安全性設計不僅僅表現在某一個部件方面,而是表現在整體方案方面,包括邏輯設計、物理實現都應該考慮。從邏輯上,各種加密算法、CPU 的狀態設置及MMU 實現、算法函數實現時間的隨機化、具有真隨機數發生器、頻率檢測、電壓檢測、溫度檢測等,都屬于安全性設計的范疇。從物理實現上,防止各種物理解剖、探測都是安全性設計應該考慮的措施。

1.3.6 其它一些發展

在功耗方面,現階段接觸卡ISO7816 規范的定義是100ma(Class A),但是一些實際的行業規范都比ISO7816 規范嚴格,比如SIM 卡,由

于是電池供電,一般要求工作電流<10ma)。對于非接觸卡,受到射頻信號的影響,對芯片功耗的要求比接觸卡更為嚴格,低功耗設計是一個挑戰。

關于電源電壓,受到手持設備應用的驅動,芯片供電電壓范圍也在發展,發展趨勢是5V —> 3V —> 1.8V,為了兼容機具,要求智能卡的端口支持較寬的端口電平范圍,比如5V-2.7V 等。

1、 軟、硬件結合

2、 項目的交付件:除了芯片外,還應該完成開發系統的設計與開發,具有配套的輔助產品(開發系統、仿真器、軟掩膜卡、一些支持COS 開發的算法函數/系統函數、配套的讀卡器)

3、 芯片只是一個平臺,在其上開發不同的COS,就形成不同的產品。

4、 在產品整個生命周期中,會源源不斷地有新COS 應用在芯片平臺上。不同的COS 通過掩膜寫入在ROM 中

二、 智能卡的設計方法

智能卡芯片是一個SOC 的解決方案,與之對應,CPU 智能卡的設計開發方法就與一般的集成電路芯片設計有所不同,有一個方法學的概念。

1、CPU 卡的存儲器包括:ROM(COS)、EEPROM/EFLASH(支持程序下載)、RAM(或XRAM)、支持SFR 擴展。一般都具有MMU機制。

2、智能卡設計包括兩大方面:即功能設計、安全性設計。安全性設計是智能卡的一個必要的設計內容,這是智能卡設計與一般的SOC設計的最大區別。

安全性設計不是項目中某一階段、某一個工程師的責任,而是一個整體解決方案,是設計過程中軟件、硬件、算法、設計實現都必須考慮的設計要素,必須貫穿整個設計、生產、項目管理過程中。

3、CPU 是芯片的核心,所有的算法協處理器(DES、RSA、ECC、CRC 等)、通訊接口(ISO7816、typeA、typeB RF 接口、USB 接口、包括一些通用IO 接口)、安全模塊(TRNG、VD、FD、TD 等)都作為CPU 的外設,通過SFR 總線與CPU 相接。

4、芯片的邏輯驗證基本上是通過編寫不同的ASM 程序,裝入ROM或EEPROM,進行仿真驗證。

5、 在設計的總體設計及創建階段,必須考慮到開發系統的實現及其支持能力。開發系統具有兩個主要功能(作用),一是作為芯片的FPGA 驗證手段;二是作為COS 開發平臺,供COS 開發人員使用。

6、 應該考慮把軟開發系統作為設計的必要組成部分,尤其在各種算法的軟、硬件劃分還沒有完全確定的時候,軟開發系統能在設計的較早期階段,對方案進行評估,進行設計優化。

7、 芯片的技術規范(datasheet)必須在設計的早期完成(隨著設計的創建完成,基本同步完成),以便于COS 開發人員盡早介入到項目中。

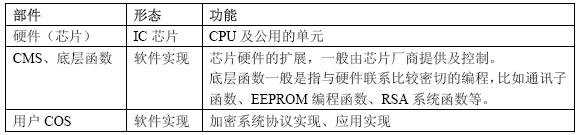

8、 隨著設計復雜度的增加,設計必須按層次結構的方式組織。一般可以分為三個層次:1)IP 設計開發(包括模擬IP、數字IP、定制IP、軟IP 等),2)芯片整合或集成(以CPU 為核心)和3)COS 開發并與芯片配合形成具體的產品。

第一層的設計是為第二層的設計服務,在其設計階段、文檔完成過程中,都應該清楚其服務對象是第二層,并支持第二層的設計實現。

第二層的設計是為第三層的設計服務,在其設計階段、文檔完成過程中,都應該清楚其服務對象是第三層,并支持第三層的設計實現。

每個層次之間的接口、文檔都必須清晰,從使用者的角度完成技術規范(datasheet)。

各個IP 及CPU 的開發相互獨立、并行進行,原理上是并在芯片的整合開始之前完成,但是一個IP 可以整合到芯片中(為了并行開

發)的基本前提條件是:

具備明確的接口信號定義、時序關系定義,

具有技術規范(Datasheet)

對應的仿真模型(.V)

一個IP 可以發布(release)(可以開始芯片實現設計)的前提條件是:

具備明確的接口信號定義、時序關系定義,

具有技術規范(Datasheet)

對應的仿真模型(.V)

在IP 設計師所假設的仿真(模擬)條件下,通過仿真(模擬)。

對應軟IP,必須是可綜合的

對于硬IP,必須具備綜合庫模型.db 等等。